## (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

*H10K* 19/00 (2023.01) *H01L* 29/66 (2006.01) *H01L* 29/788 (2006.01) *H10K* 10/00 (2023.01)

(52) CPC특허분류

H10K 19/10 (2023.02) H01L 29/66825 (2013.01)

(21) 출원번호 **10-2021-0121144**

(22) 출원일자 **2021년09월10일** 심사청구일자 **2021년09월10일**

(65) 공개번호 10-2023-0037971 (43) 공개일자 2023년03월17일

(56) 선행기술조사문헌

S. Lee. et al., Nature Communications 8(1) (2017. 9. 30.)\*

H. Yoo. et al, Adv. Mater. 31, 1808265 (2019. 5. 22.)\*

KR1020160052807 A

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2023년09월15일

(11) 등록번호 10-2578614

(24) 등록일자 2023년09월11일

(73) 특허권자

### 한국과학기술원

대전광역시 유성구 대학로 291(구성동)

#### 가천대학교 산학협력단

경기도 성남시 수정구 성남대로 1342 (복정동)

(72) 발명자

#### 임성갑

대전광역시 유성구 대학로 291 (구성동, 한국과학 기술원)

## 유호천

경기도 성남시 수정구 성남대로 1342 (*뒷면에 계속*)

(74) 대리인 **양성보**

전체 청구항 수 : 총 15 항

심사관 : 김진우

### (54) 발명의 명칭 플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법

#### (57) 요 약

플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법이 제시된다. 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로 제작 방법은, 이종 접합 트랜지스터를 준비하는 단계; 및 상기 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 조절하는 플래시 메모리 소자를 집적하는 단계를 포함하고, 상기 이종 접합 트랜지스터 및 상기 플래시 메모리 소자가 포함된 상기 상보를 이루는 트랜지스터를 포함하여 삼진 논리회로를 구성할 수 있다.

### 대 표 도 - 도4

(52) CPC특허분류

이충열

**H01L 29/788** (2013.01) **H10K 10/484** (2023.02) 대전광역시 유성구 대학로 291 (구성동, 한국과학 기술원)

(72) 발명자

최준환

대전광역시 유성구 대학로 291 (구성동, 한국과학 기술원)

이창현

대전광역시 유성구 대학로 291 (구성동, 한국과학 기술원)

이 발명을 지원한 국가연구개발사업

과제고유번호 1711139066

과제번호2016R1A5A100992622부처명과학기술정보통신부

과제관리(전문)기관명 한국연구재단

연구사업명 이공분야기초연구사업

연구과제명 (N01210081)(통합EZ)웨어러블 플랫폼소재 기술센터(2021년도)

기 여 율 1/3

과제수행기관명 한국과학기술원

연구기간 2021.01.01 ~ 2021.12.31

이 발명을 지원한 국가연구개발사업

과제고유번호 1711132180

교제번호 2021R1A2B5B0300141611 부처명 과학기술정보통신부

과제관리(전문)기관명 한국연구재단

연구사업명 이공분야기초연구사업

연구과제명 (N01210722)(통합EZ)이온성/극성 고분자 박막 기반 고성능 소재 개발 및 응용 (202

1년도)

기 여 율 1/3

과제수행기관명 한국과학기술원

연구기간 2021.03.01 ~ 2022.02.28

이 발명을 지원한 국가연구개발사업

과제고유번호 1711139699

과제번호2020R1A2C1101647부처명과학기술정보통신부

과제관리(전문)기관명 한국연구재단 연구사업명 개인기초연구

연구과제명 광검출과 정보저장이 동시에 가능한 플로팅-게이트 센서 소자 개발

기 여 율 1/3 과제수행기관명 가천대학교

연구기간 2020.09.01 ~ 2021.08.31

공지예외적용 : 있음

## 명 세 서

## 청구범위

#### 청구항 1

플래시 메모리를 포함하는 삼진 논리회로 제작 방법에 있어서,

이종 접합 트랜지스터를 준비하는 단계; 및

상기 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 조절하는 플래시 메모리 소자를 집적 하는 단계

를 포함하고,

상기 이종 접합 트랜지스터 및 상기 플래시 메모리 소자가 포함된 상기 상보를 이루는 트랜지스터를 포함하여 삼진 논리회로를 구성하며, 상기 삼진 논리회로의 중간 논리값은 상기 트랜지스터에 인가되는 전압에 의해 결정 되는, 삼진 논리회로 제작 방법.

#### 청구항 2

제1항에 있어서,

상기 플래시 메모리 소자를 집적하는 단계는,

상기 상보를 이루는 트랜지스터에 플로팅 게이트(floating gate)를 포함하는 플래시 메모리 소자를 집적하여 삼 진 인버터 소자를 형성하는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

### 청구항 3

제1항에 있어서.

상기 플래시 메모리 소자를 집적하는 단계는,

상기 상보를 이루는 트랜지스터에 프로그래밍 전압을 조절하여 채널 전도도를 미세 조절함에 따라 삼진 논리회 로의 중간 논리값을 미세 제어하는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

### 청구항 4

제1항에 있어서,

상기 플래시 메모리 소자를 집적하는 단계는,

상기 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상기 상보를 이루는 트랜지스터의 채널 전도도를 기설정된 차이 이하의 유사한 수준으로 구현하는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

#### 청구항 5

제1항에 있어서,

상기 플래시 메모리 소자를 집적하는 단계는,

상기 이종 접합 트랜지스터 및 상기 상보를 이루는 트랜지스터의 채널 전도도를 동일하게 맞추고, 삼진 인버터의 중간 논리값을 기설정된 값으로 최적화하는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

#### 청구항 6

제1항에 있어서,

개시제를 이용한 화학기상증착(initiated Chemical Vapor Deposition, iCVD) 공정 기반의 고분자 절연 소재를 활용하며, p형 및 n형 유기물 반도체 소재를 이용하는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

#### 청구항 7

제1항에 있어서,

상기 플래시 메모리 소자를 집적하는 단계는,

상기 플래시 메모리에서 게이트에 걸어준 프로그래밍 전압은 게이트 커플링 비율(Gate Coupling Ratio)에 따라 블로킹 절연막(Blocking Dielectric Layer)의 전기장과 터널링 절연막(Tunneling Dielectric Layer)에 걸리는 전기장(Electric Field)으로 나눠지게 되고, 상기 게이트 커플링 비율은 상기 블로킹 절연막의 유전 상수에 비례하고, 상기 터널링 절연막의 유전 상수에 반비례하는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

### 청구항 8

제7항에 있어서,

상기 플래시 메모리 소자를 집적하는 단계는,

상기 블로킹 절연막에 고유전율 절연 소재를 사용하여 상기 터널링 절연막에 더 큰 전기장이 걸리도록 설계함에 따라 상기 프로그래밍 전압을 낮추는 것

을 특징으로 하는, 삼진 논리회로 제작 방법.

#### 청구항 9

플래시 메모리를 포함하는 삼진 논리회로에 있어서,

이종 접합 트랜지스터; 및

채널 전도도를 조절하는 플래시 메모리 소자가 집적되는 상기 이종 접합 트랜지스터와 상보를 이루는 트랜지스 터

를 포함하고,

상기 삼진 논리회로의 중간 논리값은 상기 트랜지스터에 인가되는 전압에 의해 결정되는, 삼진 논리회로.

### 청구항 10

제9항에 있어서,

상기 상보를 이루는 트랜지스터는,

플로팅 게이트(floating gate)를 포함하는 상기 플래시 메모리 소자를 집적하여 삼진 인버터 소자를 형성하는 것

을 특징으로 하는, 삼진 논리회로.

### 청구항 11

제9항에 있어서,

상기 상보를 이루는 트랜지스터에 프로그래밍 전압을 조절하여 채널 전도도를 미세 조절함에 따라 삼진 논리회로의 중간 논리값을 미세 제어하는 것

을 특징으로 하는, 삼진 논리회로.

#### 청구항 12

제9항에 있어서,

상기 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상기 상보를 이루는 트랜지스터의 채널 전도도를 기설정된 차이 이하의 유사한 수준으로 구현하는 것

을 특징으로 하는, 삼진 논리회로.

#### 청구항 13

제9항에 있어서,

상기 이종 접합 트랜지스터 및 상기 상보를 이루는 트랜지스터의 채널 전도도를 동일하게 맞추고, 삼진 인버터의 중간 논리값을 기설정된 값으로 최적화하는 것

을 특징으로 하는, 삼진 논리회로.

#### 청구항 14

제9항에 있어서,

개시제를 이용한 화학기상증착(initiated Chemical Vapor Deposition, iCVD) 공정 기반의 고분자 절연 소재를 활용하며, p형 및 n형 유기물 반도체 소재를 이용하는 것

을 특징으로 하는, 삼진 논리회로.

### 청구항 15

제9항에 있어서,

상기 플래시 메모리에서 게이트에 걸어준 프로그래밍 전압은 게이트 커플링 비율(Gate Coupling Ratio)에 따라 블로킹 절연막(Blocking Dielectric Layer)의 전기장과 터널링 절연막(Tunneling Dielectric Layer)에 걸리는 전기장(Electric Field)으로 나눠지게 되고, 상기 게이트 커플링 비율은 상기 블로킹 절연막의 유전 상수에 비례하고, 상기 터널링 절연막의 유전 상수에 반비례하는 것

을 특징으로 하는, 삼진 논리회로.

### 발명의 설명

## 기술분야

[0001] 아래의 실시예들은 플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법에 관한 것으로, 더욱 상세하게는 이 종 접합 트랜지스터와 상보를 이루는 트랜지스터에 플래시 메모리 구조를 도입한 플래시 메모리를 포함하는 삼 진 논리회로 및 제작 방법에 관한 것이다.

#### 배경기술

- [0002] 최근 인공지능, 사물인터넷 등의 스마트 기술이 발전함에 따라 방대한 양의 데이터를 처리할 수 있는 고집적 반도체 기술이 요구되고 있다. 산업에서는 희로를 구성하는 단위 소자의 크기를 줄이는 초미세 공정을 통해 집적도를 향상하고 있으나 단위 소자의 크기를 무한정 줄이는 데에는 한계가 있다. 특히, 유기물 소재, 이차원 소재 등 차세대 반도체 물질로 주목 받고 있는 소재 기반의 전자소자는 기존 리소그래피(lithography) 기반의 패터닝 공정에 적합하지 않을 수 있다. 따라서 웨어러블(wearable) 전자소자에서 방대한 데이터를 처리할 수 있는 반도체 소자 기술이 필요하다.

- [0003] 현재 반도체 기기는 0과 1의 구별된 정보를 이용하는 2진법(Binary)을 사용하고 있다. 이에 반해, 다진법 논리 적용 시 기존 2진 논리에 비해 같은 데이터를 처리하는데 필요한 논리 수가 비약적으로 감소될 수 있다. 예를 들어, 0, 1, 2의 3가지 정보를 이용하는 삼진법(Ternary) 논리회로 기술을 이용하면, 같은 데이터를 처리하는데 필요한 전자소자의 개수가 기존 논리회로와 비교하여 log2/log3 = 63.1%만큼 감소할 수 있다.

- [0004] 즉, 삼진법 논리회로가 적용된다면 소자의 크기를 줄이지 않고도 집적도를 비약적으로 향상할 수 있다.

하지만, 기존 기술에서는 삼진 논리 회로 구동을 위해서는 1개의 추가 논리 상태를 만들어내기 위해 추가적인 트랜지스터가 필요했기 때문에 활용 가치가 떨어졌다. 예컨대 3진 인버터의 경우 4개의 추가 트랜지스터가 필 요하고, 총 6개의 트랜지스터로 인버터를 구동해야 한다.

[0005] 한국공개특허 10-2017-0093547호는 이러한 그래핀 트랜지스터 및 이를 이용한 3진 논리 소자에 관한 것으로, 채널 영역을 형성하는 그래핀을 특정의 도전형으로 도핑한 트랜지스터 및 이들을 조합하여 3진 데이터를 형성할수 있는 논리 소자에 관한 기술을 기재하고 있다.

### 선행기술문헌

### 특허문헌

[0006] (특허문헌 0001) 한국공개특허 10-2017-0093547호

## 발명의 내용

## 해결하려는 과제

- [0007] 실시예들은 플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법에 관하여 기술하며, 보다 구체적으로 플래시 메모리 소자를 도입하여 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 정밀하게 조절할 수 있는 기술을 제공한다.

- [0008] 실시예들은 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 플래시 메모리 구조를 도입함으로써, 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상보를 이루는 반대쪽 트랜지스터의 채널 전도도를 비슷한 수준으로 구현할 수 있는 플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법을 제공하는데 있다.

### 과제의 해결 수단

- [0009] 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로 제작 방법은, 이종 접합 트랜지스터를 준비하는 단계; 및 상기 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 조절하는 플래시 메모리 소자를 집적하는 단계를 포함하고, 상기 이종 접합 트랜지스터 및 상기 플래시 메모리 소자가 포함된 상기 상보를 이루는 트랜지스터를 포함하여 삼진 논리회로를 구성할 수 있다.

- [0010] 상기 플래시 메모리 소자를 집적하는 단계는, 상기 상보를 이루는 트랜지스터에 플로팅 게이트(floating gate) 를 포함하는 플래시 메모리 소자를 집적하여 삼진 인버터 소자를 형성할 수 있다.

- [0011] 상기 플래시 메모리 소자를 집적하는 단계는, 상기 상보를 이루는 트랜지스터에 프로그래밍 전압을 조절하여 채널 전도도를 미세 조절함에 따라 삼진 논리회로의 중간 논리값을 미세 제어할 수 있다.

- [0012] 상기 플래시 메모리 소자를 집적하는 단계는, 상기 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구 간에서의 채널 전도도와 상기 상보를 이루는 트랜지스터의 채널 전도도를 기설정된 차이 이하의 유사한 수준으로 구현할 수 있다.

- [0013] 상기 플래시 메모리 소자를 집적하는 단계는, 상기 이종 접합 트랜지스터 및 상기 상보를 이루는 트랜지스터의 채널 전도도를 동일하게 맞추고, 삼진 인버터의 중간 논리값을 기설정된 값으로 최적화할 수 있다.

- [0014] 개시제를 이용한 화학기상증착(initiated Chemical Vapor Deposition, iCVD) 공정 기반의 고분자 절연 소재를 활용하며, p형 및 n형 유기물 반도체 소재를 이용할 수 있다.

- [0015] 상기 플래시 메모리 소자를 집적하는 단계는, 상기 플래시 메모리에서 게이트에 걸어준 프로그래밍 전압은 게이트 커플링 비율(Gate Coupling Ratio)에 따라 블로킹 절연막(Blocking Dielectric Layer)의 전기장과 터널링 절연막(Tunneling Dielectric Layer)에 걸리는 전기장(Electric Field)으로 나눠지게 되고, 상기 게이트 커플링 비율은 상기 블로킹 절연막의 유전 상수에 비례하고, 상기 터널링 절연막의 유전 상수에 반비례할 수 있다.

- [0016] 상기 플래시 메모리 소자를 집적하는 단계는, 상기 블로킹 절연막에 고유전율 절연 소재를 사용하여 상기 터널링 절연막에 더 큰 전기장이 걸리도록 설계함에 따라 상기 프로그래밍 전압을 낮출 수 있다.

- [0017] 다른 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로는, 이종 접합 트랜지스터; 및 채널 전도도를 조절하는 플래시 메모리 소자가 집적되는 상기 이종 접합 트랜지스터와 상보를 이루는 트랜지스터를 포함하여 이루어질 수 있다.

- [0018] 상기 상보를 이루는 트랜지스터는, 플로팅 게이트(floating gate)를 포함하는 상기 플래시 메모리 소자를 집적하여 삼진 인버터 소자를 형성할 수 있다.

- [0019] 상기 상보를 이루는 트랜지스터에 프로그래밍 전압을 조절하여 채널 전도도를 미세 조절함에 따라 삼진 논리회로의 중간 논리값을 미세 제어할 수 있다.

- [0020] 상기 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상기 상보를 이루는 트랜지스터의 채널 전도도를 기설정된 차이 이하의 유사한 수준으로 구현할 수 있다.

- [0021] 상기 이종 접합 트랜지스터 및 상기 상보를 이루는 트랜지스터의 채널 전도도를 동일하게 맞추고, 삼진 인버터의 중간 논리값을 기설정된 값으로 최적화할 수 있다.

- [0022] 개시제를 이용한 화학기상증착(initiated Chemical Vapor Deposition, iCVD) 공정 기반의 고분자 절연 소재를 활용하며, p형 및 n형 유기물 반도체 소재를 이용할 수 있다.

- [0023] 상기 플래시 메모리에서 게이트에 걸어준 프로그래밍 전압은 게이트 커플링 비율(Gate Coupling Ratio)에 따라 블로킹 절연막(Blocking Dielectric Layer)의 전기장과 터널링 절연막(Tunneling Dielectric Layer)에 걸리는 전기장(Electric Field)으로 나눠지게 되고, 상기 게이트 커플링 비율은 상기 블로킹 절연막의 유전 상수에 비례하고, 상기 터널링 절연막의 유전 상수에 반비례할 수 있다.

#### 발명의 효과

[0024] 실시예들에 따르면 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 플래시 메모리 구조를 도입함으로써, 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상보를 이루는 반대쪽 트랜지스터의 채널 전도도를 비슷한 수준으로 구현할 수 있는 플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법을 제공할 수 있다.

### 도면의 가단한 설명

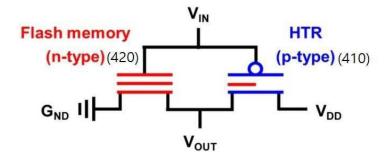

- [0025] 도 1a은 일 실시예에 따른 이종 접합 트랜지스터의 구조를 나타내는 도면이다.

- 도 1b는 일 실시예에 따른 이종 접합 트랜지스터의 전기적 특성을 나타내는 도면이다.

- 도 2는 일 실시예에 따른 이종 접합 트랜지스터를 이용하여 구현된 중간 논리 상태를 나타내는 도면이다.

- 도 3은 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로 제작 방법을 나타내는 흐름도이다.

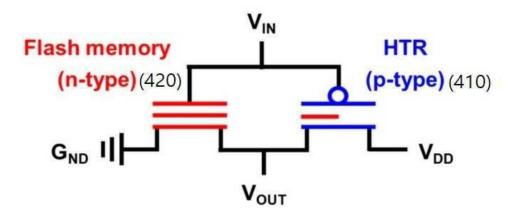

- 도 4는 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로의 평면 구조를 나타내는 도면이다.

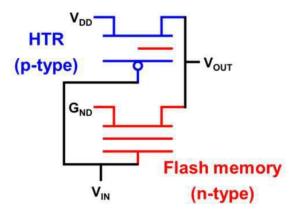

- 도 5는 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로의 수직 집적 구조를 나타내는 도면이다.

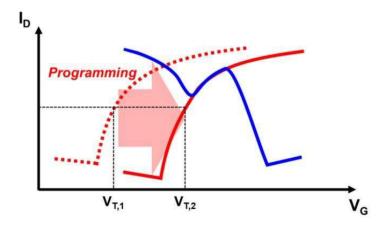

- 도 6은 일 실시예에 따른 플래시 메모리 도입을 통한 채널 전도도 조절을 나타내는 도면이다.

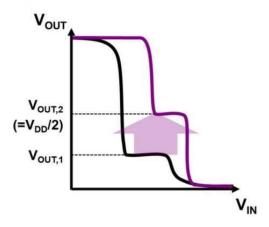

- 도 7은 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로의 중간 논리값 조절을 나타내는 도면이다.

- 도 8은 일 실시예에 따른 고분자 절연 소재 및 유기물 반도체 소재의 화학 구조를 나타내는 도면이다.

- 도 9a는 일 실시예에 따른 플래시 메모리의 투과전자현미경 이미지를 나타내는 도면이다.

- 도 9b는 일 실시예에 따른 이종 접합 트랜지스터의 투과전자현미경 이미지를 나타내는 도면이다.

- 도 9c는 일 실시예에 따른 수직 집적화된 삼진 논리회로의 투과전자현미경 이미지를 나타내는 도면이다.

- 도 10a는 일 실시예에 따른 플래시 메모리의 구조를 나타내는 도면이다.

- 도 10b는 일 실시예에 따른 11개의 플래시 메모리 소자의 트랜스퍼 특성을 나타내는 도면이다.

- 도 10c는 일 실시예에 따른 추출된 문턱전압 및 온오프 전류 비율을 나타내는 도면이다.

- 도 10d는 일 실시예에 따른 이종 접합 트랜지스터의 구조를 나타내는 도면이다.

- 도 10e는 일 실시예에 따른 11개의 이종 접합 트랜지스터의 트랜스퍼 특성을 나타내는 도면이다.

- 도 10f는 일 실시예에 따른 추출된 음의 트랜스컨덕턴스 길이 및 피크투밸리 전류 비율을 나타내는 도면이다.

- 도 10g는 일 실시예에 따른 제작된 삼진 논리회로의 전압 전달 특성을 나타내는 도면이다.

- 도 10h는 일 실시예에 따른 직류 이득 프로필을 나타내는 도면이다.

- 도 10i는 일 실시예에 따른 중간 논리값과 직류 이득 값을 나타내는 도면이다.

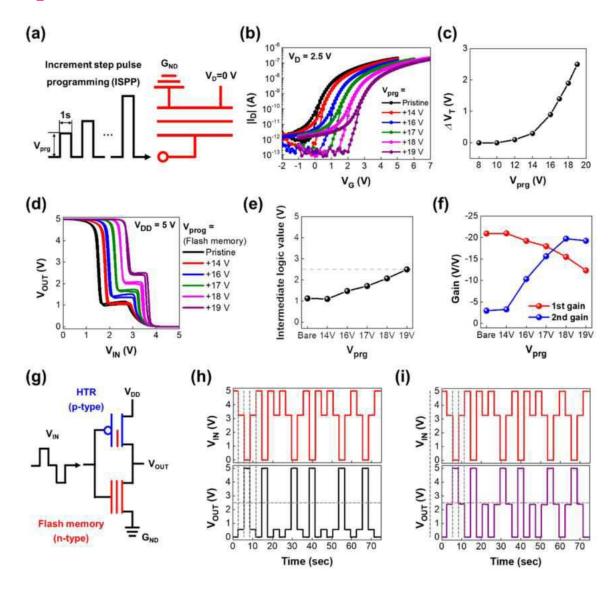

- 도 11a는 일 실시예에 따른 플래시 메모리의 증분 스텝 펄스 프로그래밍 개요도를 나타내는 도면이다.

- 도 11b는 일 실시예에 따른 프로그래밍 전압에 따른 트랜스퍼 커브 변화를 나타내는 도면이다.

- 도 11c는 일 실시예에 따른 문턱전압 이동을 나타내는 도면이다.

- 도 11d는 일 실시예에 따른 플래시 메모리 프로그래밍 전압 증가에 따른 전압 전달 특성 변화를 나타내는 도면 이다.

- 도 11e는 일 실시예에 따른 중간 논리값을 나타내는 도면이다.

- 도 11f는 일 실시예에 따른 직류 이득 값 변화를 나타내는 도면이다.

- 도 11g는 일 실시예에 따른 트랜션트 측정 개요도를 나타내는 도면이다.

- 도 11h는 일 실시예에 따른 프로그래밍 되지 않은 상태에서의 측정 결과를 나타내는 도면이다.

- 도 11i는 일 실시예에 따른 프로그래밍 된 상태(프로그래밍 전압 19 V)에서의 측정 결과를 나타내는 도면이다.

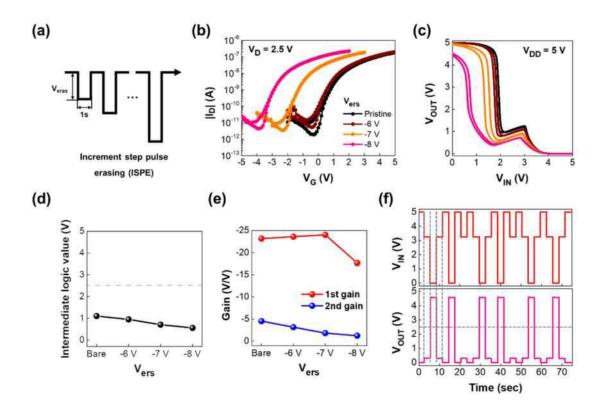

- 도 12a는 일 실시예에 따른 증분 스텝 펄스 이레이징의 개요도를 나타내는 도면이다.

- 도 12b는 일 실시예에 따른 이레이징 전압에 따른 트랜스퍼 커브 변화를 나타내는 도면이다.

- 도 12c는 일 실시예에 따른 전압 전달 특성 변화를 나타내는 도면이다.

- 도 12d는 일 실시예에 따른 중간 논리값을 나타내는 도면이다.

- 도 12e는 일 실시예에 따른 직류 이득 값 변화를 나타내는 도면이다.

- 도 12f는 일 실시예에 따른 이레이징 된 상태(이레이징 전압 -8 V)에서의 트랜션트 측정 결과를 나타내는 도면이다.

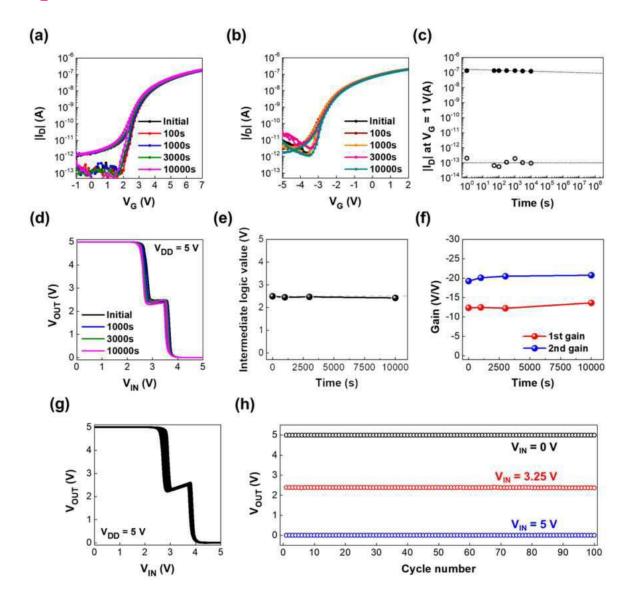

- 도 13a는 일 실시예에 따른 프로그래밍을 나타내는 도면이다.

- 도 13b는 일 실시예에 따른 이레이징 후 시간에 따른 트랜스퍼 특성 변화를 나타내는 도면이다.

- 도 13c는 일 실시예에 따른 시간에 따른 드레인 전류 변화를 나타내는 도면이다.

- 도 13d는 일 실시예에 따른 플래시 메모리의 최적 프로그래밍 상태에서의 삼진 논리회로의 전압 전달 특성을 나타내는 도면이다.

- 도 13e는 일 실시예에 따른 중간 논리값을 나타내는 도면이다.

- 도 13f는 일 실시예에 따른 직류 이득 값 변화를 나타내는 도면이다.

- 도 13g는 일 실시예에 따른 반복 동작에 따른 삼진 논리회로의 전압 전달 특성 변화를 나타내는 도면이다.

- 도 13h는 일 실시예에 따른 0, 3.25, 5 V의 입력 전압에서의 출력 전압 변화를 나타내는 도면이다.

## 발명을 실시하기 위한 구체적인 내용

- [0026] 이하, 첨부된 도면을 참조하여 실시예들을 설명한다. 그러나, 기술되는 실시예들은 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 이하 설명되는 실시예들에 의하여 한정되는 것은 아니다. 또한, 여러 실시예들은 당해 기술분야에서 평균적인 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다. 도면에서 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있다.

- [0028] 아래의 실시예들은 플래시 메모리 소자를 도입하여 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널

전도도를 정밀하게 조절할 수 있는 기술을 제공한다.

- [0029] 실시예들은 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상보를 이루는 반대쪽 트랜지스터의 채널 전도도를 비슷한 수준으로 구현하기 위해 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 플래시 메모리 구조를 도입하였다. 플래시 메모리 구조를 도입하면 프로그래밍 전압에 따라 채널 전도도를 정밀하게 조절할 수 있기 때문에 삼진 논리회로의 가장 중요한 특성인 중간 논리 상태를 정밀하게 조절할 수 있다.

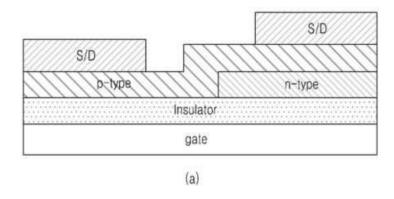

- [0031] 도 1a는 일 실시예에 따른 이종 접합 트랜지스터의 구조를 나타내는 도면이고, 도 1b는 일 실시예에 따른 이종 접합 트랜지스터의 전기적 특성을 나타내는 도면이다.

- [0032] 도 1a를 참조하면, 이종 접합 트랜지스터(heterojunction transistor, HTR)는 서로 다른 두 반도체 층이 접합을 이루고 있는 형태의 소자이다. 즉, 이종 접합 트랜지스터(HTR)는 p형 반도체와 n형 반도체가 서로 부분적으로 접합되어 있는 형태로 구성된다.

- [0033] 도 1b에 도시된 바와 같이, 이종 접합 트랜지스터(HTR)는 p형 반도체가 두 소스 및 드레인(S/D)을 연결하는 반면, n형 반도체는 한 개의 소스 또는 드레인에만 영향을 받기 때문에 해당 트랜지스터를 구동하게 되면, 단조 증가함수를 보이는 기존 트랜지스터와는 다르게 특정 구간에서 게이트 전압이 증가함에도 불구하고 드레인 전류가 감소하게 된다.

- [0034] 즉, 이종 접합 트랜지스터(HTR)는 특정 게이트 전압(gate voltage,  $V_0$ ) 구간에서 전압이 증가할수록 전류가 감소하는 음의 트랜스컨덕턴스(negative transconductance, NTC)를 나타낸다.

- [0035] 해당 트랜지스터는 p형 반도체가 소스/드레인과 모두 접촉하고 있기 때문에, p형 트랜지스터처럼 구동시켜야 높은 온/오프(on/off) 전류 비와 함께 음의 트랜스컨덕턴스 특성을 보이며 정상 작동한다. p형 트랜지스터 구동 방식으로 작동시키면, 낮은 게이트 전압에서는 n형 반도체가 축적(accumulation) 상태가 되고, 높은 게이트 전압에서는 p형 반도체가 축적(accumulation) 상태가 되는데, 게이트 전압이 증가함에 따라 n형 반도체는 디플리션(depletion)되는데 반해, p형 반도체가 축적(accumulation)되어 처음에는 전류가 증가하다가 n형 반도체의 디플리션(depletion)으로 인해 전류가 감소하는 음의 트랜스컨덕턴스 구간이 발생하게 된다. 하지만, 결국 p형 반도체가 축적(accumulation)되면서, 다시 전류가 증가하는 N 모양의 전압 및 전류 곡선이 만들어진다.

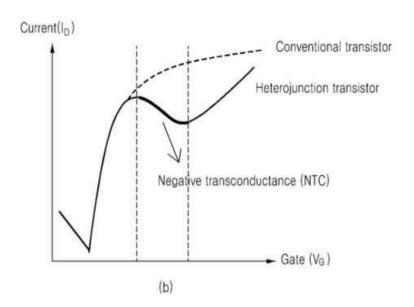

- [0037] 도 2는 일 실시예에 따른 이종 접합 트랜지스터를 이용하여 구현된 중간 논리 상태를 나타내는 도면이다.

- [0038] 기존 Complementary 인버터(inverter)를 구성하는 하나의 트랜지스터를 이종 접합 트랜지스터로 대체하면, 도 2 에 도시된 바와 같이, 음의 트랜스컨덕턴스가 발생하는 구간에서 두 트랜지스터가 비슷한 수준의 저항을 갖게되어 0과 1 사이의 새로운 논리 상태가 발생한다. 이러한 이종 접합 트랜지스터를 이용하여 삼진법 논리 체계를 구현하게 되면 소자의 복잡성 없이도 논리회로를 비약적으로 향상할 수 있기 때문에, 이종 접합 트랜지스터를 이용한 삼진법 소자에 대한 연구가 활발히 진행되어 왔다.

- [0039] 현재 보고된 삼진 인버터는 대부분 비대칭 범위의 input voltage( $V_{\rm IN}$ ), output voltage( $V_{\rm OUT}$ )으로 작동되고 있으며, 특히 중간 논리값이 이상적인 값( $V_{\rm ID}$ 의 절반 값  $\sim V_{\rm ID}/2$ )에 미치지 못하고 있다. 중간 논리값이 이상적인 값에 도달하기 위해서는 음의 트랜스컨덕턴스 구간에서 두 트랜지스터가 비슷한 수준의 채널 전도도(channel conductance)를 가져야 하지만, 채널 전도도는 각 트랜지스터를 구성하는 전극, 절연막, 반도체 소재에 따라 달라지기 때문에 채널 전도도를 비슷한 수준으로 맞추기에 어려움이 따른다. 특히, 이종 접합 트랜지스터는 서로다른 두 반도체 물질로 구성되기 때문에 음의 트랜스컨덕턴스 구간과 해당 구간에서의 채널 전도도를 디자인하기 매우 어렵다.

- [0040] 따라서 이러한 어려움을 극복하기 위해 본 실시예에서는 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 정밀하게 조절할 수 있는 플래시 메모리 소자를 도입하였다.

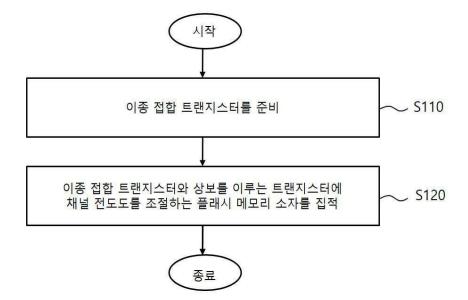

- [0042] 도 3은 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로 제작 방법을 나타내는 흐름도이다.

- [0043] 도 3을 참조하면, 일 실시예에 따른 컴퓨터 장치에 의해 수행되는 플래시 메모리를 포함하는 삼진 논리회로 제작 방법은, 이종 접합 트랜지스터를 준비하는 단계(S110), 및 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 조절하는 플래시 메모리 소자를 집적하는 단계(S120)를 포함하고, 이종 접합 트랜지스터 및 플래시 메모리 소자가 포함된 상보를 이루는 트랜지스터를 포함하여 삼진 논리회로를 구성할 수 있다.

- [0045] 단계(S110)에서, 이종 접합 트랜지스터를 준비할 수 있다.

- [0046] 그리고, 단계(S120)에서, 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 채널 전도도를 조절하는 플래시 메모리 소자를 집적할 수 있다. 이에 따라 이종 접합 트랜지스터 및 플래시 메모리 소자가 포함된 상보를 이루는 트랜지스터를 포함하여 삼진 논리회로를 구성할 수 있다.

- [0047] 여기서, 상보를 이루는 트랜지스터에 플로팅 게이트(floating gate)를 포함하는 플래시 메모리 소자를 집적하여 삼진 인버터 소자를 형성할 수 있다. 그리고, 상보를 이루는 트랜지스터에 프로그래밍 전압을 조절하여 채널 전도도를 미세 조절함에 따라 삼진 논리회로의 중간 논리값을 미세 제어할 수 있다.

- [0048] 이에 따라 이종 접합 트랜지스터의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상보를 이루는 트랜지스터의 채널 전도도를 기설정된 차이 이하의 유사한 수준으로 구현할 수 있다. 특히, 이종 접합 트랜지스터 및 상보를 이루는 트랜지스터의 채널 전도도를 동일하게 맞추고, 삼진 인버터의 중간 논리값을 기설정된 값으로 최적화할 수 있다.

- [0049] 이 때, 이종 접합 트랜지스터 및 상보를 이루는 트랜지스터는 개시제를 이용한 화학기상증착(initiated Chemical Vapor Deposition, iCVD) 공정 기반의 고분자 절연 소재를 활용하며, p형 및 n형 유기물 반도체 소재를 이용할 수 있다.

- [0050] 플래시 메모리에서 게이트에 걸어준 프로그래밍 전압은 게이트 커플링 비율(Gate Coupling Ratio)에 따라 블로킹 절연막(Blocking Dielectric Layer)의 전기장과 터널링 절연막(Tunneling Dielectric Layer)에 걸리는 전기장(Electric Field)으로 나눠지게 되고, 게이트 커플링 비율은 블로킹 절연막의 유전 상수에 비례하고, 터널링 절연막의 유전 상수에 반비례할 수 있다. 이에 따라 블로킹 절연막에 고유전율 절연 소재를 사용하여 터널링절연막에 더 큰 전기장이 걸리도록 설계함에 따라 프로그래밍 전압을 낮출 수 있다.

- [0051] 실시예들은 이종 접합 트랜지스터와 상보를 이루는 트랜지스터에 플래시 메모리 구조를 도입하였으며, 이를 통해 프로그래밍 전압을 조절하여 채널 전도도를 정밀하게 조절함에 따라 중간 논리 상태를 정밀하게 제어할 수있는 플래시 메모리를 포함하는 삼진 논리회로 및 제작 방법을 제공한다.

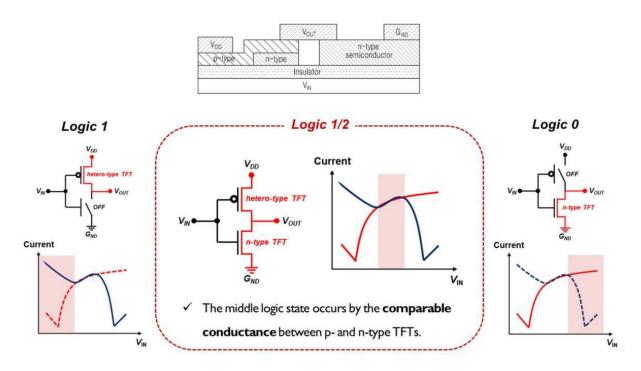

- [0053] 도 4는 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로의 평면 구조를 나타내는 도면이고, 도 5는 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로의 수직 집적 구조를 나타내는 도면이다.

- [0054] 도 4 및 도 5를 참조하면, 이종 접합 트랜지스터와 상보를 이루는 반대쪽 트랜지스터에 플로팅 게이트(floating gate)를 포함하는 플래시 메모리 소자를 도입하였다. 도 4는 평면 구조에서, 도 5는 수직 적층 구조에서 플래시 메모리를 집적한 삼진 인버터 소자의 회로도이다.

- [0056] 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로 제작 방법을 이용하여 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로를 제작할 수 있다. 아래에서는 도 4를 예를 들어 플래시 메모리를 포함하는 삼 진 논리회로를 설명한다.

- [0057] 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로는 이종 접합 트랜지스터(HTR, 410), 및 채널 전도도를 조절하는 플래시 메모리 소자가 집적되는 이종 접합 트랜지스터와 상보를 이루는 트랜지스터(420)를 포함하여 이루어질 수 있다.

- [0058] 상보를 이루는 트랜지스터(420)는 플로팅 게이트를 포함하는 플래시 메모리 소자를 집적하여 삼진 인버터 소자를 형성할 수 있다. 이러한 상보를 이루는 트랜지스터(420)에 프로그래밍 전압을 조절하여 채널 전도도를 미세 조절함에 따라 삼진 논리회로의 중간 논리값을 미세 제어할 수 있다.

- [0059] 이에 따라 이종 접합 트랜지스터(410)의 음의 트랜스컨덕턴스가 나타나는 구간에서의 채널 전도도와 상보를 이루는 트랜지스터(420)의 채널 전도도를 기설정된 차이 이하의 유사한 수준으로 구현할 수 있으며, 특히 이종 접합 트랜지스터(410) 및 상보를 이루는 트랜지스터(420)의 채널 전도도를 동일하게 맞추고, 삼진 인버터의 중간 논리값을 기설정된 값으로 최적화할 수 있다.

- [0060] 한편, 이종 접합 트랜지스터(410) 및 상보를 이루는 트랜지스터(420)는 개시제를 이용한 화학기상증착(iCVD) 공 정 기반의 고분자 절연 소재를 활용하며, p형 및 n형 유기물 반도체 소재를 이용할 수 있다.

- [0061] 플래시 메모리에서 게이트에 걸어준 프로그래밍 전압은 게이트 커플링 비율에 따라 블로킹 절연막의 전기장과 터널링 절연막에 걸리는 전기장으로 나눠지게 되고, 게이트 커플링 비율은 블로킹 절연막의 유전 상수에 비례하

- 고, 터널링 절연막의 유전 상수에 반비례할 수 있다.

- [0063] 도 6은 일 실시예에 따른 플래시 메모리 도입을 통한 채널 전도도 조절을 나타내는 도면이다.

- [0064] 플래시 메모리를 도입하면, 도 6에 도시된 바와 같이, 한쪽 트랜지스터의 문턱전압을 정밀하게 제어할 수 있고, 이를 통해 음의 트랜스컨덕턴스 구간에서 두 트랜지스터의 채널 전도도를 동일하게 맞출 수 있다.

- [0065] 도 7은 일 실시예에 따른 플래시 메모리를 포함하는 삼진 논리회로의 중간 논리값 조절을 나타내는 도면이다.

- [0066] 따라서, 도 7에 도시된 바와 같이, 두 트랜지스터의 채널 전도도를 맞춤으로써 삼진 인버터의 중간 논리값을 이 상적인 값(~½)으로 최적화할 수 있다.

- [0068] 본 실시예에서는 개시제를 이용한 화학기상증착(initiated Chemical Vapor Deposition, iCVD) 공정 기반의 고 분자 절연 소재를 활용하였다. 반도체 물질은 우수한 전기적 특성을 가진 p형 dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene(DNTT)와 n형 N,N'-ditridecylperylene-3,4,9,10-tetracarboxylic diimide(PTCDI-C13) 유기물 반도체 소재를 활용하였다. 또한, 소자의 집적도를 더욱 향상하기 위해, 도 7에 도시된 바와 같은, 수직 집적 구조를 활용하였다. 하지만 플래시 메모리를 이용한 삼진 논리회로는 소재와 소자에 관계없이 구현할 수 있다. 즉, 수직 집적 구조에 국한되지 않고 평면 구조에도 활용될 수 있으며, 유기물 소재뿐만 아니라 산화물 반도체, 이차원 반도체 및 무기물 절연 소재 등을 이용하여서도 구현할 수 있다.

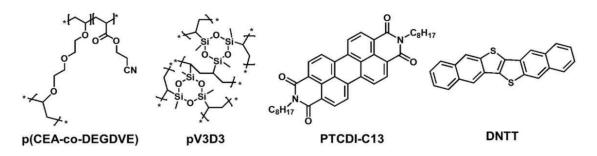

- [0069] 도 8은 일 실시예에 따른 고분자 절연 소재 및 유기물 반도체 소재의 화학 구조를 나타내는 도면이다.

- [0070] 도 8을 참조하면, 일 실시예에서 사용한 고분자 절연막 및 유기물 반도체 소재의 화학 구조를 나타낸다.

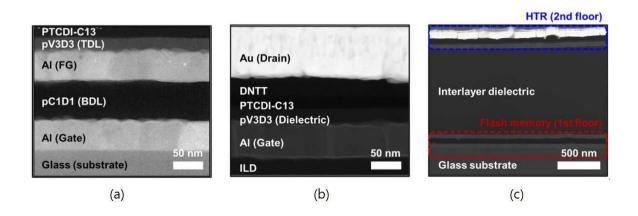

- [0071] 도 9a는 일 실시예에 따른 플래시 메모리의 투과전자현미경 이미지를 나타내는 도면이고, 도 9b는 일 실시예에 따른 이종 접합 트랜지스터의 투과전자현미경 이미지를 나타내는 도면이며, 도 9c는 일 실시예에 따른 수직 집 적화된 삼진 논리회로의 투과전자현미경 이미지를 나타내는 도면이다.

- [0072] 도 9a 내지 도 9c에 도시된 바와 같이, 투과전자현미경(Transmission Electron Microscope, TEM)을 이용하여 소자의 수직 집적 구조를 분석하였다.

- [0074] 도 10a는 일 실시예에 따른 플래시 메모리의 구조를 나타내는 도면이고, 도 10b는 일 실시예에 따른 11개의 플래시 메모리 소자의 트랜스퍼 특성을 나타내는 도면이며, 도 10c는 일 실시예에 따른 추출된 문턱전압 및 온오 프 전류 비율을 나타내는 도면이다. 또한, 도 10d는 일 실시예에 따른 이종 접합 트랜지스터의 구조를 나타내는 도면이고, 도 10e는 일 실시예에 따른 11개의 이종 접합 트랜지스터의 트랜스퍼 특성을 나타내는 도면이며, 도 10f는 일 실시예에 따른 추출된 음의 트랜스컨덕턴스 길이 및 피크투밸리 전류 비율을 나타내는 도면이다. 또한, 도 10g는 일 실시예에 따른 제작된 삼진 논리회로의 전압 전달 특성을 나타내는 도면이고, 도 10h는 일 실시예에 따른 직류 이득 프로필을 나타내는 도면이며, 도 10i는 일 실시예에 따른 중간 논리값과 직류 이득 값을 나타내는 도면이다.

- [0075] 도 10a를 참조하면, 일 실시예에 따른 제작된 플래시 메모리 소자의 구조를 나타낸다. 일 실시예에 따르면 p형 트랜지스터에 이종 접합 트랜지스터를 도입하고, n형 트랜지스터에 플래시 메모리 구조를 도입하였으나, 반대의 경우도 가능하다. 다시 말하면, n형 트랜지스터에 이종 접합 트랜지스터를 도입하고, p형 트랜지스터에 플래시 메모리 구조를 도입할 수 있다.

- [0076] 플래시 메모리에서 게이트에 걸어준 프로그래밍/이레이징 전압은 게이트 커플링 비율(Gate Coupling Ratio, a R)에 따라 블로킹 절연막(Blocking Dielectric Layer, BDL)의 전기장과 터널링 절연막(Tunneling Dielectric Layer, TDL)에 걸리는 전기장(Electric Field, E)으로 나눠지게 된다(ETDL/EBDL). 이러한 게이트 커플링 비율은 블로킹 절연막의 유전 상수에 비례하고, 터널링 절연막의 유전 상수에 반비례한다.

- [0077] 일 실시예에서는 블로킹 절연막에 고유전율 절연 소재(poly(2-cyanoethyl acrylate-co-diethylene glycol divinyl ether, p(CEA-co-DEGDVE), 최적화된 조성: pClD1)를 도입하고, 터널링 절연막에 저유전율 절연 소재 (poly(1,3,5-trivinyl-1,3,5-trimethyl cyclotrisiloxane), pV3D3)를 도입하여 터널링 절연막에 더 큰 전기장이 걸리도록 설계함으로써 프로그래밍/이레이징 전압을 낮추고자 하였다.

- [0078] 도 10b에 도시된 바와 같이, 제작된 11개의 플래시 메모리 소자는 균일한 트랜스퍼 특성(transfer characteristics)을 나타내었으며, 이를 통해 도 10c에 도시된 바와 같이, 균일한 문턱전압(threshold voltage,  $V_1$ ), 온오프 전류비(current on/off ratio,  $I_{on}/I_{off}$ )를 얻을 수 있었다. 도 10d에 도시된 바와 같이,

이종 접합 트랜지스터는 저유전율 pV3D3 고분자 절연막 및 PTCDI-C13, DNTT 유기 반도체를 기반으로 제작되었으며, 도 10e 및 도 10f에 도시된 바와 같이, 이종 접합 트랜지스터 또한 우수한 전기적 특성과 성능 균일도를 나타내었다.

- [0079] 특히, 중간 논리값을 유도하는 음의 트랜스컨덕턴스 현상이 모든 소자에서 나타났으며, 음의 트랜스컨덕턴스 길이는 1.09 ± 0.10V, 피크투밸리 전류비(peak-to-valley current ratio)는 12.04 ± 4.43으로 균일한 음의 트랜스컨덕턴스 특성을 나타내었다. 도 10g 및 도 10h에 도시된 바와 같이, 각 단위소자의 우수한 균일도로 인해제작된 삼진 논리회로 또한 균일한 전압전달특성(Voltage Transfer Characteristic, VTC) 및 직류 이득 프로필(DC gain profile)을 나타내었다. 특히, 모든 삼진 논리회로는 분명한 중간 논리 상태를 나타내었으며, 도 10i에 도시된 바와 같이 균일한 중간 논리값과 직류 이득 값을 나타내었다.

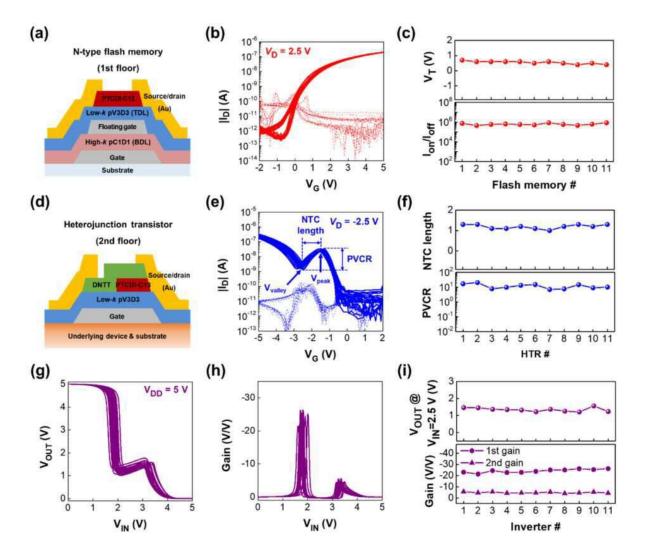

- [0081] 도 11a는 일 실시예에 따른 플래시 메모리의 증분 스텝 펄스 프로그래밍 개요도를 나타내는 도면이고, 도 11b는 일 실시예에 따른 프로그래밍 전압에 따른 트랜스퍼 커브 변화를 나타내는 도면이며, 도 11c는 일 실시예에 따른 문턱전압 이동을 나타내는 도면이다. 또한, 도 11d는 일 실시예에 따른 플래시 메모리 프로그래밍 전압 증가에 따른 전압 전달 특성 변화를 나타내는 도면이고, 도 11e는 일 실시예에 따른 중간 논리값을 나타내는 도면이며, 도 11f는 일 실시예에 따른 직류 이득 값 변화를 나타내는 도면이다. 또한, 도 11g는 일 실시예에 따른 트랜션트 측정 개요도를 나타내는 도면이고, 도 11h는 일 실시예에 따른 프로그래밍 되지 않은 상태에서의 측정 결과를 나타내는 도면이며, 도 11i는 일 실시예에 따른 프로그래밍 된 상태(프로그래밍 전압 19 V)에서의 측정 결과를 나타내는 도면이다.

- [0082] 플래시 메모리의 게이트 전극에 양의 전압 또는 음의 전압을 가해서 플로팅 게이트에 전자를 저장하거나 플로팅 게이트로부터 전자를 탈트랩(detrap) 시킴으로써 플래시 메모리의 전기적 특성을 분석하였다.

- [0083] 도 11a를 참조하면, 플래시 메모리의 프로그래밍/이레이징 윈도우(programming/erasing window)를 증분 스텝 필스 프로그래밍 또는 이레이징(incremental step pulse programming/erasing, ISPP/ISPE)을 통해 분석하였다. 또한, 도 11b를 참조하면, 프로그래밍 전압이 증가함에 따라 트랜스퍼 커브(transfer curve)가 양전압 방향으로 순차적으로 이동하였다. 도 11c를 참조하면, 문턱전압은 12 V의 낮은 프로그래밍 전압을 걸어주었을 때부터 이동하기 시작하였으며, 이는 높은 게이트 커플링 비율 덕분이다. 최대 19 V 프로그래밍 전압을 걸어주었을 때문턱전압은 2.5 V 이동하였으며, 이는 낮은 동작 전압(5 V)을 고려하였을 때 큰 프로그래밍 윈도우라고 볼 수있다.

- [0084] 플래시 메모리의 프로그래밍 상태에 따라 삼진 논리회로의 전압 전달 특성을 분석하였다. 도 11d에 도시된 바와 같이, 프로그래밍 전압이 증가함에 따라 삼진 논리회로의 전압 전달 특성에서 중간 논리값이 순차적으로 증가함을 확인할 수 있었다. 이는 프로그래밍 전압이 증가함에 따라 n형 트랜지스터의 채널 전도도가 감소하여 이종 접합 트랜지스터의 음의 트랜스컨덕턴스 구간에서 두 트랜지스터가 비슷한 수준의 채널 전도도를 나타내기 때문이다.

- [0085] 특히, 도 11e에 도시된 바와 같이, 19 V의 프로그래밍 전압에서 중간 논리값(2.49 V)은 이상적인 값(2.5 V)에 근접하였다. 프로그래밍 전압이 증가함에 따라 첫 번째 직류 이득은 순차적으로 감소하였으며, 두 번째 직류 이득은 순차적으로 감소하였고, 이는 도 11f에 도시된 바와 같이, 중간 논리값이 증가하기 때문이다.

- [0086] 개발된 삼진 논리회로의 실질적인 응용 가능성을 검증하기 위해 트랜션트 측정(transient measurement)을 진행하였다. 도 11g를 참조하면, 트랜션트 측정 개요도를 나타낸다. 도 11h에 도시된 바와 같이, 프로그래밍 되지않은 상태에서는 작은 중간 논리값을 나타내는 데 비해, 도 11i에 도시된 바와 같이, 플래시 메모리가 최적화프로그래밍 된 상태에서는 이상적인 값에 근접한 중간 논리값을 나타내었다. 이를 통해 플래시 메모리의 채널전도도를 조절하여 삼진 논리회로의 전기적인 특성을 최적화할 수 있음을 검증하였다.

- [0088] 도 12a는 일 실시예에 따른 증분 스텝 펄스 이레이징의 개요도를 나타내는 도면이고, 도 12b는 일 실시예에 따른 이레이징 전압에 따른 트랜스퍼 커브 변화를 나타내는 도면이며, 도 12c는 일 실시예에 따른 전압 전달 특성 변화를 나타내는 도면이다. 또한, 도 12d는 일 실시예에 따른 중간 논리값을 나타내는 도면이고, 도 12e는 일 실시예에 따른 직류 이득 값 변화를 나타내는 도면이며, 도 12f는 일 실시예에 따른 이레이징 된 상태(이레이징 전압 -8 V)에서의 트랜션트 측정 결과를 나타내는 도면이다.

- [0089] 도 12a를 참조하면, 증분 스텝 펄스 이레이징에 따른 플래시 메모리와 삼진 논리회로의 전기적 특성 변화 또한 분석하였다. 또한, 도 12b를 참조하면, 이레이징 전압이 증가함에 따라 플래시 메모리의 트랜스퍼 특성은 음의

방향으로 순차적으로 이동하였다. 프로그래밍에서와는 반대로 프로그래밍을 이레이징할 시 삼진 논리회로의 전기적 특성이 저해되었으며, 특히, 도 12c에 도시된 바와 같이, -8 V의 이레이징 전압을 가해주었을 때에는  $V_{OUT}$ 의 완전한 스윙(full-swing)이 저해되었다. 이는 이레이징에 따라 n형 트랜지스터의 채널 전도도가 p형 트랜지스터의 채널 전도도보다 압도적으로 높아지기 때문이다.

- [0090] 도 12d 및 도 12e에 도시된 바와 같이, 이레이징 전압이 증가함에 따라 중간 논리값과 두 번째 직류 이득은 감소하였다. 첫 번째 직류 이득은 증가하다가 -8 V의 이레이징 전압에서 감소하였는데, 이는 -8 V 이레이징에서 Vour의 완전한 스윙(full-swing)이 저해되기 때문이다. 도 12f에 도시된 바와 같이, 이레이징된 상태에서 트랜션트 측정을 진행한 결과 프로그래밍/이레이징되지 않은 초기 상태와 비교해서도 더 작은 중간 논리값을 나타내었고, 이는 도 12c에 나타낸 결과와 일치한다.

- [0092] 도 13a는 일 실시예에 따른 프로그래밍을 나타내는 도면이고, 도 13b는 일 실시예에 따른 이레이징 후 시간에 따른 트랜스퍼 특성 변화를 나타내는 도면이며, 도 13c는 일 실시예에 따른 시간에 따른 드레인 전류 변화를 나타내는 도면이다. 또한, 도 13d는 일 실시예에 따른 플래시 메모리의 최적 프로그래밍 상태에서의 삼진 논리회로의 전압 전달 특성을 나타내는 도면이고, 도 13e는 일 실시예에 따른 중간 논리값을 나타내는 도면이며, 도 13f는 일 실시예에 따른 직류 이득 값 변화를 나타내는 도면이다. 또한, 도 13g는 일 실시예에 따른 반복 동작에 따른 삼진 논리회로의 전압 전달 특성 변화를 나타내는 도면이고, 도 13h는 일 실시예에 따른 0, 3.25, 5 V의 입력 전압에서의 출력 전압 변화를 나타내는 도면이다.

- [0093] 플래시 메모리의 전기적 특성 최적화에 따라 삼진 논리회로의 성능이 최적화될 수 있음을 검증하였으나, 최적화된 선 성능이 유지되는 것 또한 중요하다. 다시 말해서, 플래시 메모리의 리텐션 특성(retention characteristic)과 이에 따른 삼진 논리회로의 특성 변화 검증이 필요하다. 먼저, 도 13a 및 도 13b에 도시된 바와 같이, 플래시 메모리를 최대 프로그래밍/이레이징 전압(각각 19, -8 V)을 가한 후에 트랜스퍼 특성 변화를 관찰하였다. 온 상태(이레이징 상태)에서 드레인 전류(drain current,  $I_D$ )는 100, 1000, 10000 초 이후에도 각각 초기 드레인 전류의 1.004, 0.999, 0.911배를 나타내어 우수한 리텐션 특성을 나타내었다. 도 13c에 도시된 바와 같이, 외삽을 통해 10년 후의 드레인 전류를 예측한 결과 1 크기 정도(order of magnitude) 이하의 변화만을 나타내었다.

- [0094] 도 13d를 참조하면, 플래시 메모리의 우수한 리텐션 특성으로 인해 삼진 논리회로 또한 시간에 따라 전기적 특성 변화가 거의 나타나지 않았다. 도 13e에 도시된 바와 같이, 중간 논리값은 1000, 3000, 10000 초 이후에도 각각 2.45, 2.47, 2.42 V를 나타내어 이상적인 값에 가까운 중간 논리 값이 유지되고 있음을 확인할 수 있었다. 또한, 도 13f에 도시된 바와 같이, 첫 번째, 두 번째 직류 이득 값 또한 거의 변화하지 않음을 확인할 수 있었다(10000 초 동안 1.5 V/V 이하의 변화).

- [0095] 도 13g를 참조하면, 삼진 논리회로의 반복적인 동작에 따른 전기적 특성 변화를 관찰한 결과를 나타내고, 도 13h를 참조하면, 100번의 반복적인 동작에도 전압 전달 특성과 입력 전압에 따른 출력 전압이 거의 변화하지 않아 우수한 동작 안정성을 검증할 수 있었다.

- [0097] 기존 유기물 기반의 이종 접합 트랜지스터는 p형 반도체와 n형 반도체가 채널 중앙 영역에서만 접합되는 형태의 구조를 나타내어 낮은 온/오프 전류 비율을 나타내었고, 이로 인해 삼진 논리회로에서 출력 전압의 완전한 스윙을 얻기 어려웠다. 이러한 단점을 극복하기 위해 하나의 반도체 층이 소스/드레인 전극과 모두 접촉하는 형태의 이종 접합 트랜지스터가 개발되었으며 개발된 삼진 논리회로는 출력전압의 완전한 스윙을 나타내었다.

- [0098] 본 실시예에서는 플래시 메모리 소자를 도입하여 중간 논리 값을 이상적인 값으로 최적화할 수 있는 방법을 제시하였다. 게다가 초박막 절연 소재와 소재 디자인을 통해 낮은 구동전압 및 프로그래밍/이레이징 전압에서 구동할 수 있는 삼진 논리회로를 제공하였다.

- [0099] 이상과 같이, 실시예들에 따르면 플래시 메모리 구조를 도입하여 삼진 논리회로의 중간 논리 상태 및 출력 값을 정밀하게 조절하였다. 실시예들은 단순히 플래시 메모리 소자를 도입하는 설계 차원의 기술이기 때문에 사용하는 물질에 관계없이 다양한 종류의 트랜지스터에 적용할 수 있다. 특히, 최근 주목 받는 웨어러블 전자소자 분야에서 각광받고 있는 유기물 반도체, 산화물 반도체, 이차원 소재 등 다양한 이종 접합 트랜지스터와 삼진 논리회로에 적용할 수 있다.

- [0101] 이상과 같이 실시예들이 비록 한정된 실시예와 도면에 의해 설명되었으나, 해당 기술분야에서 통상의 지식을 가진 자라면 상기의 기재로부터 다양한 수정 및 변형이 가능하다. 예를 들어, 설명된 기술들이 설명된 방법과 다

른 순서로 수행되거나, 및/또는 설명된 시스템, 구조, 장치, 회로 등의 구성요소들이 설명된 방법과 다른 형태로 결합 또는 조합되거나, 다른 구성요소 또는 균등물에 의하여 대치되거나 치환되더라도 적절한 결과가 달성될수 있다.

[0102] 그러므로, 다른 구현들, 다른 실시예들 및 특허청구범위와 균등한 것들도 후술하는 특허청구범위의 범위에 속한 다.

[0103]

도면

도면4

## 도면8

도면11